# Modicon Momentum 170 AEC 920 00 User Manual

Schneider Gelectric

(Original Document)

12/2018

The information provided in this documentation contains general descriptions and/or technical characteristics of the performance of the products contained herein. This documentation is not intended as a substitute for and is not to be used for determining suitability or reliability of these products for specific user applications. It is the duty of any such user or integrator to perform the appropriate and complete risk analysis, evaluation and testing of the products with respect to the relevant specific application or use thereof. Neither Schneider Electric nor any of its affiliates or subsidiaries shall be responsible or liable for misuse of the information contained herein. If you have any suggestions for improvements or amendments or have found errors in this publication, please notify us.

You agree not to reproduce, other than for your own personal, noncommercial use, all or part of this document on any medium whatsoever without permission of Schneider Electric, given in writing. You also agree not to establish any hypertext links to this document or its content. Schneider Electric does not grant any right or license for the personal and noncommercial use of the document or its content, except for a non-exclusive license to consult it on an "as is" basis, at your own risk. All other rights are reserved.

All pertinent state, regional, and local safety regulations must be observed when installing and using this product. For reasons of safety and to help ensure compliance with documented system data, only the manufacturer should perform repairs to components.

When devices are used for applications with technical safety requirements, the relevant instructions must be followed.

Failure to use Schneider Electric software or approved software with our hardware products may result in injury, harm, or improper operating results.

Failure to observe this information can result in injury or equipment damage.

© 2018 Schneider Electric. All rights reserved.

### **Table of Contents**

|   | $\square$ |

|---|-----------|

| 5 |           |

| Part I<br>Chapter 1 | Safety Information.       About the Book.         About the Book.       1         Function Overview       1         Introduction.       1         Introduction       1         Function Mode and Application Range       1 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2           | Description of the Operating Modes                                                                                                                                                                                         |

|                     | Overview of the Operating Modes                                                                                                                                                                                            |

|                     | Common Counter Properties                                                                                                                                                                                                  |

|                     | Count Channel for Count Functions with Pulse and Incremental                                                                                                                                                               |

|                     | Encoder       2         Operating Modes for Pulse and Incremental Encoders       2                                                                                                                                         |

|                     | Operating Modes for Absolute Encoder                                                                                                                                                                                       |

|                     | Count Channel for Counting Functions with Absolute Encoders 3                                                                                                                                                              |

| Chapter 3           | TSX Momentum Adapter 3                                                                                                                                                                                                     |

|                     | TSX Momentum Bus Adapter                                                                                                                                                                                                   |

|                     | CPU Adapters and Interface Adapters of the TSX Momentum 3                                                                                                                                                                  |

| Part II             | Module Description 4                                                                                                                                                                                                       |

| Chapter 4           | Structure of the 170 AEC 920 4                                                                                                                                                                                             |

| •                   | Internal Connections and Meaning of Signals                                                                                                                                                                                |

|                     | Wiring and Examples 4                                                                                                                                                                                                      |

|                     | LED Status Indicators                                                                                                                                                                                                      |

|                     | Technical Data                                                                                                                                                                                                             |

|                     | Selecting a Momentum Adapter                                                                                                                                                                                               |

|                     | Selection of Terminal Blocks                                                                                                                                                                                               |

| Part III            | Configuration                                                                                                                                                                                                              |

| Chapter 5           | Configuration of Output Words                                                                                                                                                                                              |

| -                   | Configuration                                                                                                                                                                                                              |

|                     | Summary of the Output Words                                                                                                                                                                                                |

|                     | Configuring Output Words 1 and 2 6                                                                                                                                                                                         |

|                     | Configuring Output Words 3 and 4 74                                                                                                                                                                                        |

|                     | Data in Output Words 5/6 and 7/8                                                                                                                                                                                           |

|                     | File Format of Set Data                                                                                                                                                                                                    |

| Chapter 6 | Status Messages and Count Values                          | 87  |

|-----------|-----------------------------------------------------------|-----|

|           | Status and Error Bits (Words 1 and 2)                     | 88  |

|           | Status Returned (Words 3 and 4)                           | 92  |

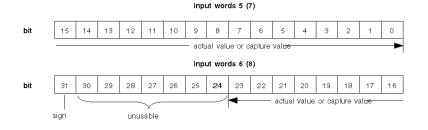

|           | Actual Values for Counters 1 and 2                        | 94  |

| Chapter 7 | Parameter Setting of the AEC Block                        | 97  |

|           | Configuring Channels on the 170 AEC 920 00 Counter Module | 98  |

|           | Brief Description.                                        | 102 |

| Chapter 8 | Application Examples                                      | 103 |

| 8.1       | Up Counter (Mode 2)                                       | 104 |

|           | Example 1                                                 | 105 |

|           | Solution                                                  | 106 |

| 8.2       | Up Counter with Preset Value                              | 110 |

|           | Task Specification                                        | 111 |

|           | Solution                                                  | 112 |

| 8.3       | Up Counter with Internal Clock Pulse                      | 118 |

|           | Task Specification                                        | 119 |

|           | Solution                                                  | 120 |

| 8.4       | Pulse Counter with External Time Base                     | 126 |

|           | Example 4                                                 | 127 |

|           | Solution                                                  | 129 |

| 8.5       | Period Meter with Internal Time Base                      | 134 |

|           | Task Specification                                        | 135 |

|           | Solution                                                  | 137 |

| Index     |                                                           | 141 |

|           |                                                           |     |

### Safety Information

#### **Important Information**

#### NOTICE

Read these instructions carefully, and look at the equipment to become familiar with the device before trying to install, operate, service, or maintain it. The following special messages may appear throughout this documentation or on the equipment to warn of potential hazards or to call attention to information that clarifies or simplifies a procedure.

The addition of this symbol to a "Danger" or "Warning" safety label indicates that an electrical hazard exists which will result in personal injury if the instructions are not followed.

This is the safety alert symbol. It is used to alert you to potential personal injury hazards. Obey all safety messages that follow this symbol to avoid possible injury or death.

###

**DANGER** indicates a hazardous situation which, if not avoided, **will result in** death or serious injury.

### A WARNING

**WARNING** indicates a hazardous situation which, if not avoided, **could result in** death or serious injury.

##

**CAUTION** indicates a hazardous situation which, if not avoided, **could result** in minor or moderate injury.

### NOTICE

NOTICE is used to address practices not related to physical injury.

#### PLEASE NOTE

Electrical equipment should be installed, operated, serviced, and maintained only by qualified personnel. No responsibility is assumed by Schneider Electric for any consequences arising out of the use of this material.

A qualified person is one who has skills and knowledge related to the construction and operation of electrical equipment and its installation, and has received safety training to recognize and avoid the hazards involved.

#### **BEFORE YOU BEGIN**

Do not use this product on machinery lacking effective point-of-operation guarding. Lack of effective point-of-operation guarding on a machine can result in serious injury to the operator of that machine.

### **WARNING**

#### UNGUARDED EQUIPMENT

- Do not use this software and related automation equipment on equipment which does not have point-of-operation protection.

- Do not reach into machinery during operation.

#### Failure to follow these instructions can result in death, serious injury, or equipment damage.

This automation equipment and related software is used to control a variety of industrial processes. The type or model of automation equipment suitable for each application will vary depending on factors such as the control function required, degree of protection required, production methods, unusual conditions, government regulations, etc. In some applications, more than one processor may be required, as when backup redundancy is needed.

Only you, the user, machine builder or system integrator can be aware of all the conditions and factors present during setup, operation, and maintenance of the machine and, therefore, can determine the automation equipment and the related safeties and interlocks which can be properly used. When selecting automation and control equipment and related software for a particular application, you should refer to the applicable local and national standards and regulations. The National Safety Council's Accident Prevention Manual (nationally recognized in the United States of America) also provides much useful information.

In some applications, such as packaging machinery, additional operator protection such as pointof-operation guarding must be provided. This is necessary if the operator's hands and other parts of the body are free to enter the pinch points or other hazardous areas and serious injury can occur. Software products alone cannot protect an operator from injury. For this reason the software cannot be substituted for or take the place of point-of-operation protection. Ensure that appropriate safeties and mechanical/electrical interlocks related to point-of-operation protection have been installed and are operational before placing the equipment into service. All interlocks and safeties related to point-of-operation protection must be coordinated with the related automation equipment and software programming.

**NOTE:** Coordination of safeties and mechanical/electrical interlocks for point-of-operation protection is outside the scope of the Function Block Library, System User Guide, or other implementation referenced in this documentation.

#### START-UP AND TEST

Before using electrical control and automation equipment for regular operation after installation, the system should be given a start-up test by qualified personnel to verify correct operation of the equipment. It is important that arrangements for such a check be made and that enough time is allowed to perform complete and satisfactory testing.

### **WARNING**

#### EQUIPMENT OPERATION HAZARD

- Verify that all installation and set up procedures have been completed.

- Before operational tests are performed, remove all blocks or other temporary holding means used for shipment from all component devices.

- Remove tools, meters, and debris from equipment.

#### Failure to follow these instructions can result in death, serious injury, or equipment damage.

Follow all start-up tests recommended in the equipment documentation. Store all equipment documentation for future references.

#### Software testing must be done in both simulated and real environments.

Verify that the completed system is free from all short circuits and temporary grounds that are not installed according to local regulations (according to the National Electrical Code in the U.S.A, for instance). If high-potential voltage testing is necessary, follow recommendations in equipment documentation to prevent accidental equipment damage.

Before energizing equipment:

- Remove tools, meters, and debris from equipment.

- Close the equipment enclosure door.

- Remove all temporary grounds from incoming power lines.

- Perform all start-up tests recommended by the manufacturer.

#### **OPERATION AND ADJUSTMENTS**

The following precautions are from the NEMA Standards Publication ICS 7.1-1995 (English version prevails):

- Regardless of the care exercised in the design and manufacture of equipment or in the selection and ratings of components, there are hazards that can be encountered if such equipment is improperly operated.

- It is sometimes possible to misadjust the equipment and thus produce unsatisfactory or unsafe operation. Always use the manufacturer's instructions as a guide for functional adjustments. Personnel who have access to these adjustments should be familiar with the equipment manufacturer's instructions and the machinery used with the electrical equipment.

- Only those operational adjustments actually required by the operator should be accessible to the operator. Access to other controls should be restricted to prevent unauthorized changes in operating characteristics.

### About the Book

#### At a Glance

#### **Document Scope**

This manual describes the structure and the configuration of the fast counter module AEC 920. The different operating modes are explained using the applications as examples.

#### Validity Note

This documentation is valid for EcoStruxure™ Control Expert 14.0 or later.

#### Product Related Information

### **WARNING**

#### UNINTENDED EQUIPMENT OPERATION

The application of this product requires expertise in the design and programming of control systems. Only persons with such expertise should be allowed to program, install, alter, and apply this product.

Follow all local and national safety codes and standards.

Failure to follow these instructions can result in death, serious injury, or equipment damage.

### Part I Function Overview

#### **Overview**

This part of this manual provides a brief overview of the structure, application, and various operating modes of the 170 AEC 920 00 fast counter module.

#### What Is in This Part?

This part contains the following chapters:

| Chapter | Chapter Name                       | Page |

|---------|------------------------------------|------|

| 1       | Introduction                       | 13   |

| 2       | Description of the Operating Modes | 19   |

| 3       | TSX Momentum Adapter               | 37   |

### Chapter 1 Introduction

#### Overview

This chapter contains a short overview of function mode and application range.

#### What Is in This Chapter?

This chapter contains the following topics:

| Торіс                               | Page |

|-------------------------------------|------|

| Introduction                        | 14   |

| Function Mode and Application Range | 15   |

#### Introduction

#### General Information about the 170 AEC 920 00 Counter

The 170 AEC 920 00 I/O unit is used for fast counting operations and conforms to the system properties of the Modicon Momentum family. With the addition of a bus or CPU adapter it forms an operating module.

In this book, the mode of operation of the 170 AEC 920 00 is described.

- introduction (current chapter)

- description of the operating modes (see page 19)

- hardware description of the 170 AEC 920 00 unit (see page 43)

- counter configuration (see page 63)

- status messages and numerical values (see page 87)

- DFB parameter settings (see page 97)

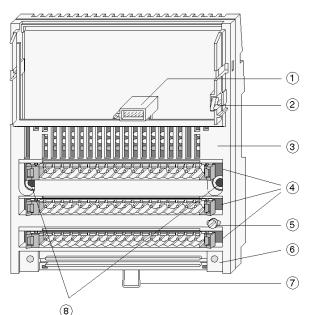

Module view

- 1 internal connector to the adapter

- 2 locking and grounding contact for the adapter

- 3 LED display field

- 4 sockets for the terminal plugs

- 5 grounding screw

- 6 installation point for busbar

- 7 locking catch for DIN rail

- 8 holes for wall mounting

#### Function Mode and Application Range

#### Use of the 170 AEC 920 00

The 170 AEC 920 00 I/O unit has two hardware counters with a maximum input frequency of 200 kHz.

They can be used for the following applications:

- event counts

- frequency measurements

- period measurements

- clock output (pulse generator)

- path evaluation using incremental encoders

The module can therefore be used to evaluate pulses and positions. To do this, one of 13 possible operating modes must be set depending on the application. See Operating Modes (see page 20).

Encoders evaluate impulses or positions and send this information on to the I/O unit. The I/O unit's firmware interprets them, depending on the operating mode, as impulses, path increments, etc. and compares them continuously with preset values. It controls two hardware outputs per counter depending on the result of this comparison. These outputs can therefore used for pre-stop and limit switch outputs.

These operating modes often demand particular types of encoder (impulse encoders, absolute encoders, or incremental encoders). The encoder input signals are 5 volt signals; 24 volt signals are also acceptable in many applications.

For the control of counting and comparison functions, each of the two counters has three additional hardware inputs that can also be used as software signals:

- enabling the counting function

- accept default value

- freeze counter value

**NOTE:** The operating modes are described in Description of Operating Modes (*see page 19*). See Configuration of Output Words (*see page 63*) and Status Messages and Count Values (*see page 87*) for the configuration and diagnostic data for these functions. Refer to Setting Parameters for the AEC DFB-Block (*see page 97*) for examples of the configuration of counter operation modes.

#### **Event Counting**

The module is suitable for the evaluation of fast count impulses and for specific reactions if preset values are exceeded in positive or negative direction.

#### **Repeating Counters (Infinite Counts)**

In this operating mode the module counts to the previously transferred modulo value and subsequently jumps to the 0 value, and counts from then on. If the value 0 is exceeded during down counting, the count value jumps to the modulo value. Only positive modulo values are acceptable.

**NOTE:** The repeating function can be activated for each operating mode by the transfer of a positive modulo value (reference number 7). The operating modes C, D, and E for absolute encoders are exceptions.

#### **Frequency Measurements**

In this operating mode, frequencies up to 200 kHz can be measured. The time base can be varied in a range from 0.1 ms to 1000 ms.

#### **Period Measurements**

In this operating mode, the duration of a period can be measured. To do this the pulses are counted for the duration of the gate time. Various time bases can be selected according to the duration of the period. There are 5 time bases available, from 1ms to 10,000 ms.

#### Clock Output (Pulse Generator)

Pulses generated through the module can be distributed through the outputs Q1 (counter 1) and Q2 (counter 2). Pulses with a pulse-width of 1 ms up to 1000 s can be distributed. See Operating Mode 8: Impulse Counter with Time Base (RPM Measurement) *(see page 28)*.

#### **Incremental Path Evaluation**

Path evaluation with incremental encoders occurs according to the counting procedure. The measuring system must therefore be reset after switching on or voltage loss (accepting preset values). The encoder then transmits a reference signal (zero impulse). In order to identify the direction of spin while turning forward or backward, the encoder sends two periodical square wave signals in quadrature, which are evaluated and counted correspondingly in the AEC.

To allow data transfer at higher frequencies, the signals can also be transmitted as differential signals corresponding to the RS 422, so that interfering impulses as well as common-mode interference can be recognized and filtered out. In this case, six lines are required for the data transfer (two each for the three-count inputs).

#### Accepting reference values (accepting preset values)

If the current positions are lost because of voltage loss or disconnection, the 170 AEC 920 00 measuring system must be reset when the voltage returns or when it is reconnected (accepting preset values). The encoder will transmit a reference signal (zero impulse) to do this.

There seven different possibilities available for the acceptance of a preset value.

An acceptance of the preset value is also necessary after every new enable of the counting channel; otherwise, the digital outputs will not be operated.

So that the point of reference is constantly approached from one direction, the reference point switch should be installed just in front of a hardware limit switch.

#### **Absolute Path Evaluation**

In absolute path evaluation, a numerical value is assigned to each position. This task is undertaken by an absolute encoder. The numerical values exist in the encoder as a code pattern (e.g. on code slices in dual code, gray code, or similar). The advantage of this type of encoder is that the absolute position is available immediately after it is switched on.

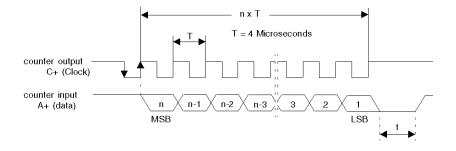

The determination of the actual position is carried out as follows:

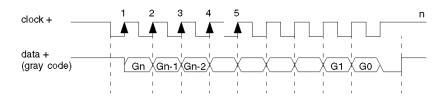

The 170 AEC 920 00 requests the position value through a clock pulse sequence. The absolute position existing in the encoder is saved with the first clocking signal of the 170 AEC 920 00 and transmitted to the 170 AEC 920 00 as a serial data telegram (Gn...G0) synchronously to the clock signal. The length of the data stream to be transmitted is dependent on the resolution and the data format of the encoder and can be defined using configuration words. With standard codes the resolution is n=24.

SSI - data and clocking telegrams

This data transfer is conducted through a synchronous serial interface of four lines (two each for clock signal and data).

To allow data transfer at higher frequencies, the signals are transmitted as differential signals corresponding to RS 422 so that interfering impulses can be identified and common-mode interference filtered out.

Introduction

### Chapter 2 Description of the Operating Modes

#### **Overview**

This chapter describes all current operating modes in which the counter can function. The operating modes for each counter are set individually over output words 1 and 2.

Further information can be found in Configuration (see page 61).

#### What Is in This Chapter?

This chapter contains the following topics:

| Торіс                                                                |    |

|----------------------------------------------------------------------|----|

| Overview of the Operating Modes                                      | 20 |

| Common Counter Properties                                            | 21 |

| Count Channel for Count Functions with Pulse and Incremental Encoder | 25 |

| Operating Modes for Pulse and Incremental Encoders                   | 26 |

| Operating Modes for Absolute Encoder                                 | 32 |

| Count Channel for Counting Functions with Absolute Encoders          | 34 |

#### **Overview of the Operating Modes**

#### Overview

The following table gives an overview of the current operating modes:

| Operating Mode | Encoder Type *) | Function                                                                                                                                                                                                                           |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | -               | Channel not ready, Parameters not reset, Output = 0                                                                                                                                                                                |

| 1              | imp             | Down counter                                                                                                                                                                                                                       |

| 2              | imp             | Up counter                                                                                                                                                                                                                         |

| 3              | ink             | corresponds with operation mode "0"                                                                                                                                                                                                |

| 4              | ink             | Up/down counter, path evaluation, 1/1-logic                                                                                                                                                                                        |

| 5              | ink             | Up/down counter, path evaluation, 4/1-logic                                                                                                                                                                                        |

| 6              | imp             | Differential counter: Counter input A = up;<br>Counter input B = down                                                                                                                                                              |

| 7              | imp             | Up counter /Down counter: Counter Input A = up/down; Counter Input<br>B = Direction (1 = up, 0 = down)                                                                                                                             |

| 8              | imp             | Impulse counter with time base (e.g. for variable speeds counting, Cv factors, etc) a) with external Clock Signal on counter input B as time base or b) digital output (Q) as time base on counter input B                         |

| 9              | imp             | Period meter with 5 time bases for full or half period, full period $0 = no$ time base, $1 = 1, 2 = 10, 3 = 100, 4 = 1000, 5 = 10000$ [micro sec]; half per $9 = 1, A = 10, B = 100, C = 1000, D = 10000$ [micro sec]              |

| A              | imp             | Frequency meter with 5 time bases for full or half period; whole period $0 = no$ time base, $1 = 0.1$ , $2 = 1$ , $3 = 10$ , $4 = 100$ , $5 = 1000$ [ms]; half period $9 = 0.1$ , $A = 1$ , $B = 10$ , $C = 100$ , $D = 1000$ [ms] |

| В              | -               | corresponds with operation mode "0"                                                                                                                                                                                                |

| С              | abs             | Path evaluation with single-turn encoders (SSI), 12 bit resolution                                                                                                                                                                 |

| D              | abs             | Path evaluation with multi-turn encoders (SSI), 24 bit resolution                                                                                                                                                                  |

| E              | abs             | Path evaluation with multi-turn encoders (SSI), 25 bit resolution                                                                                                                                                                  |

| F              | -               | Software-Reset. In this instance both counters are always set back, regardless of the operation mode for counter 1 or 2 being invoked.                                                                                             |

NOTE: \*) Explanation of encoder type:

inc = incremental encoder

abs = absolute encoder

imp = impulse encoder

**NOTE:** 0, 3, and B are not really operating modes. The counter is in Zero Status, that is, in a determinated and stable status, and it is inactive.

#### **Common Counter Properties**

#### **Counter Types**

The two counters of the 170 AEC 920 00 I/O unit can only be operated as a group, either with incremental, pulse, or absolute encoders.

#### **Counter Resolution**

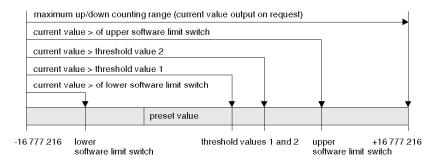

The resolution of the counter is 24 bit maximum (signed); corresponding to decimal values of -16 777 216 ... +16 777 215. The count range used is defined through the operating mode. There are thirteen operating modes available.

#### 5 V / 24 V Counter Inputs

Encoders with 5 V differential signal (RS 422) as well as encoders with 24 V signal (single-ended) can be connected to the module.

#### **Preset Value (Preset)**

With the preset value (preset) the counter can be loaded with a freely definable value from the PLC. The acceptance of the preset value is dependent on the preset mode as well as the digital inputs. In this case digital input 1 is assigned to counter 1, and digital input 4 is assigned to counter 2. If no preset value is transmitted from the PLC, then 0 is applied as the preset value in the counter.

#### Software Limit Switch

The operation range of the counter can be specified with the upper and lower software limit switch. If the limits of the software limit switch are exceeded, the digital outputs will be switched off, and an error message will be generated. The software limit switches are only active after the parameters for the upper and lower software limit switch have been transferred.

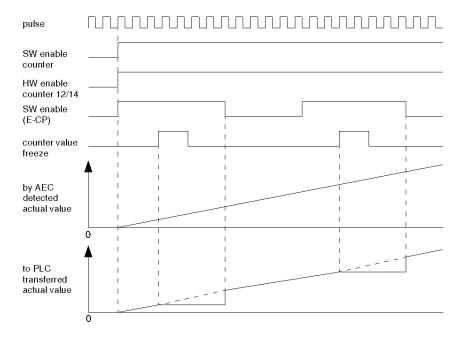

#### Freeze Current Counter Value (Capture Function)

With this function the current counter value is relayed into an additional register. The counter operates independently of this function. This function is particularly useful for measuring pulses or paths. The counter value is frozen after enabling through software (Bit E\_CP) and through an edge at hardware input I3 for counter 1 and I6 for counter 2. After the frozen counter value is accepted it is transferred to the PLC in actual values until the Bit E\_CP is reset by the software. After being reset the actual value of the counter is transmitted.

Pulse diagram of freezing counter value

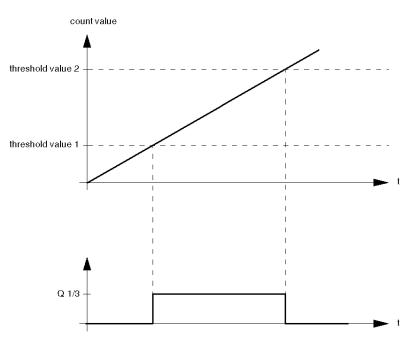

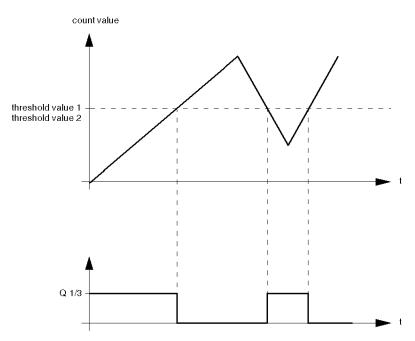

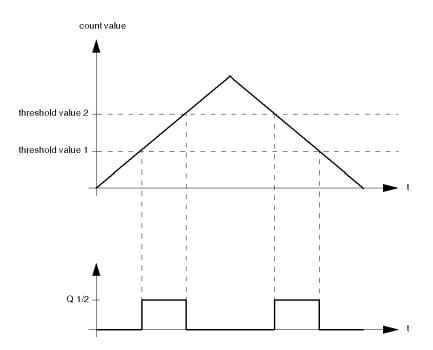

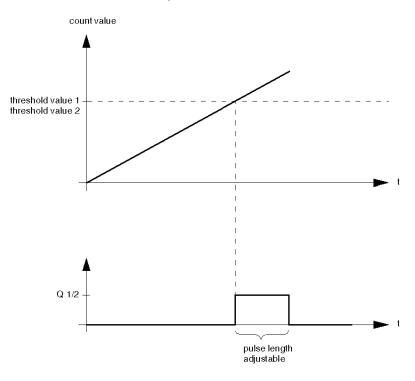

#### **Event Processing**

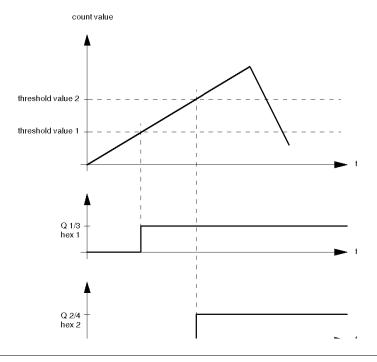

The user has the option of assigning event-controlled functions to the outputs. The digital outputs are set when the defined event has occurred.

The following events can be defined:

- counter value = threshold value 18

- counter value >= threshold value 18

- counter value <= threshold value 18

- counter value >= threshold value 1 and < threshold value 2

Further information can be found in Reference Numbers for Set Data (Output Words 3 and 4 (Bits 0 ... 4) *(see page 75)*.

The terms used in this book are explained below:

#### Definition of term

The counting pulse signals are dependent on the type of encoder. The I/O unit can process signal levels of 5V or 24V.

For this reason there are two counter inputs available for each of the two counters.

- 5V-differential signals (channels A+, A-; B+, B-; Z+, Z-)

- 24V-differential signals (channels A\*, A-; B\*, B-; Z\*, Z-)

- 24V single-ended signals (channels A\*, B\*, Z\* connected with the relationship of the encoder potential. Switch off the encoder monitor.)

#### **Digital Inputs to Control Counters**

The digital inputs (counter enable, preset value and selection of current counter status) are only effective in combination with the corresponding software signals.

**NOTE:** With 5V and 24V signals the counter inputs can operate using configurations with and without filters. When the filter is activated (used with mechanical contacts), the count frequency is reduced (max. 20 kHz).

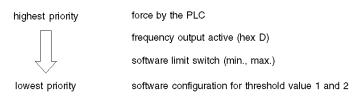

#### **Digital Outputs to Control Actuators**

The digital outputs operate in two ways:

- through configured links in the user program

- through forcing in the configuration (possible anytime)

How the outputs become effective is specified in the counter configuration. See Configuration of the Digital Outputs *(see page 77)*.

#### **Channel-specific Error Messages**

The user can obtain detailed indications as to the nature of the error at the counter input through the error word. This can be:

- error in the supply voltage for the encoder

- running over or under the measuring range

- faulty encoder

- faulty encoder connection

These errors are reported through the input word. See Status Messages and Count Values *(see page 87)*.

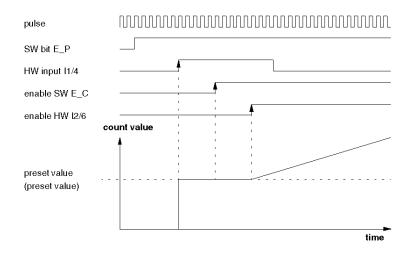

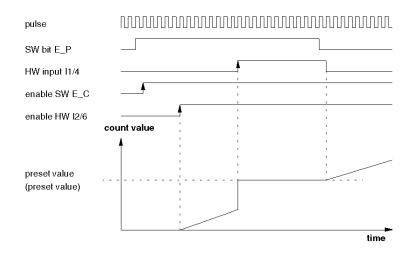

#### Receiving the Preset Value into the Counter (Preset Mode)

With the preset value (preset) the counter can be loaded with a freely definable value from the PLC. The acceptance of the preset value is dependent on the preset mode as well as the digital inputs. In this case digital input 1 is assigned to counter 1, and digital input 4 is assigned to counter 2.

The following preset modes are available:

| Preset Mode | Function                                                                                                                                                                             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | No preset value                                                                                                                                                                      |

| 1           | The preset value is accepted with a positive edge at the digital input <b>Preset</b> .                                                                                               |

| 2           | The preset value is accepted with a negative edge at the digital input <b>Preset</b> .                                                                                               |

| 3           | The preset value is accepted with a rising edge of the hardware input <b>Preset</b> . The counter has stopped. The counter starts again with the falling edge of the hardware input. |

| 4           | The preset value is accepted with a positive edge (during upward counting) or with a negative edge (during downward counting) on the digital input <b>Preset</b> .                   |

| 5           | The preset value is accepted with a negative edge (during upward counting) or with a positive edge (during downward counting) on the digital input <b>Preset</b> .                   |

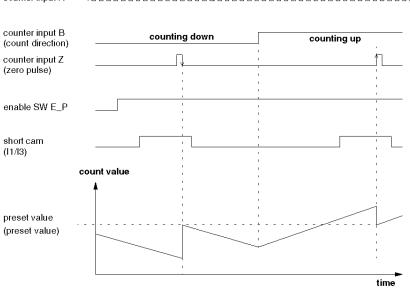

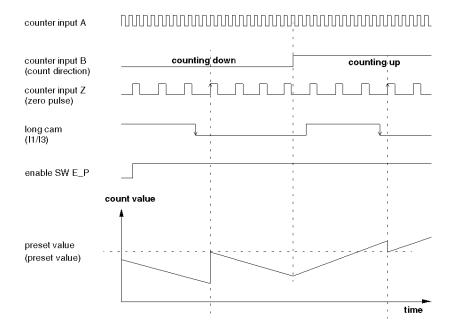

| 6           | Reference point with short cam signal                                                                                                                                                |

| 7           | Reference point with long cam signal                                                                                                                                                 |

In preset modes 6 and 7, the zero pulse from the encoder (counter input Z) is used for the reception of the preset value. The encoder gives out this counting pulse after every full rotation.

The preset mode can be set. See Preset Modes (Output Words 1 and 2 (Bits 12 ... 14) *(see page 70)*. The preset modes are not applicable in all operating modes (frequency, period and pulse counters).

### Count Channel for Count Functions with Pulse and Incremental Encoder

#### **Functional Principle**

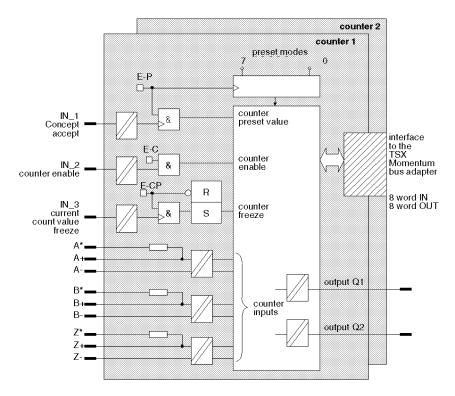

The configured links for software and hardware show the correlations for incremental encoders.

#### **Operating Modes for Pulse and Incremental Encoders**

#### Overview

Operating modes 1 ... A are described below.

#### **Operating Mode 1: Down Counter for Pulses**

In this operating mode, all pulses of counter input A are used for down counting, beginning from a preset value (default = 0). Counter input B has no function. Pulse encoders with 5V differential output as well as pulse encoders with 24V single ended output (24V initiators) can be connected. Two digital outputs can be controlled using two programmable threshold values. See the example Up Counter (Mode 2) *(see page 104)*.

#### **Operating Mode 2: Up Counter for Pulses**

In this operating mode, all pulses of counter input A are used for up counting, beginning from a preset value (default = 0). Counter input B has no function. Pulse encoders with 5V differential output as well as pulse encoders with 24V single ended output (24V initiators) can be connected. Two digital outputs can be controlled using two programmable threshold values. See the example Up Counter (Mode 2) *(see page 104)*.

#### **Operating Mode 3: Reserved**

Corresponds with operating mode 0.

#### Operating Mode 4: Counting with Incremental Encoder with 1/1 Logic

Position measurement with incremental encoders is carried out according to the counting procedure. The measuring system must therefore be reset after switching on or power failure. The encoder transmits a reference signal (zero pulse) to do this. In order to identify the direction of spin when counting up or down, the incremental encoder sends two periodical square wave signals in quadrature, which are evaluated by the 170 AEC 920. Two digital outputs can be controlled using two programmable threshold values.

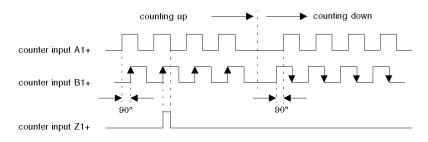

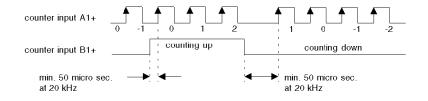

Pulse diagram of incremental encoder with 1/1 logic

#### Operating Mode 5: Counting with Incremental Encoder with 1/4 Logic

As with operating mode 4, but with fourfold resolution, as each edge of counter input A and B is evaluated. See Up Counter (Mode 2) *(see page 104)*.

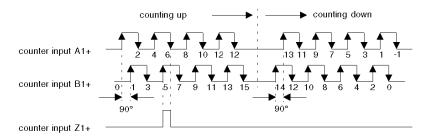

Pulse diagram of incremental encoder with 1/4 logic

NOTE: In operating modes 4 and 5, the differential signals are not displayed.

#### **Operating Mode 6: Differential Counter**

In this operating mode, all pulses at counter input A cause the counter to count up, and all pulses at counter input B cause it to count down. This means that in this operating mode the difference is established between counter input A and counter input B. Two digital outputs can be controlled using two programmable threshold values.

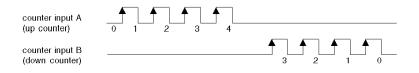

Differential counter pulse diagram

#### Operating Mode 7: Up/Down Counter with Direction Signal

In this operating mode all pulses at counter input A corresponding to the valence at counter input B are counted either up or down. With signal 1 at counter input B counting proceeds upwards, with signal 0 at counter input B counting proceeds downwards. Two digital outputs can be controlled using two programmable threshold values.

Pulse diagram of up/down counter

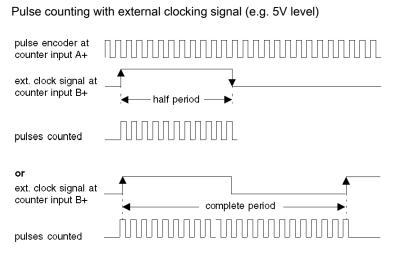

#### Operating Mode 8: Pulse Counter with Time Base (RPM Measurement)

This operating mode is suitable for determining velocities, rates of flow or rotary speeds. The pulses are counted and saved during a selected time base (gate opening time). Then the counter is reset and the counting process starts again.

The gate opening time can be controlled through two modes.

- an external clocking signal

- an internal clocking signal transmitted through digital outputs Q1 or Q3. These outputs must be configured (output words 3 and 4) as frequency outputs (Function D). The frequency must also be selected through reference number B.

The count duration results from the positive edge to the negative edge of the clocking signal (half period) or from one positive edge to the next (full period). This is also defined in output words 3 and 4.

**NOTE:** The digital inputs Accept Preset Value, Counter Enable, and Freeze Current Counter Value have no role in this operating mode. Only the frequency output function is available for the digital outputs. See Output Word 4 *(see page 75)*.

#### Example 1

**NOTE:** When an external clocking signal of a 24V level is used, the external clocking signal must be connected to counter input B\*.

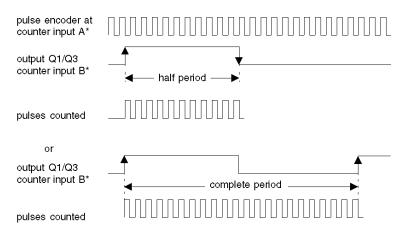

#### Example 2

Pulse counting with internal clocking signal (24V level only)

If no external clocking signal is available, digital outputs Q1/Q3 can be configured as frequency outputs. However, as the outputs are only available at 24 V level, the corresponding output Q1/Q3 must be connected with the 1M to counter input B<sup>\*</sup> and B-.

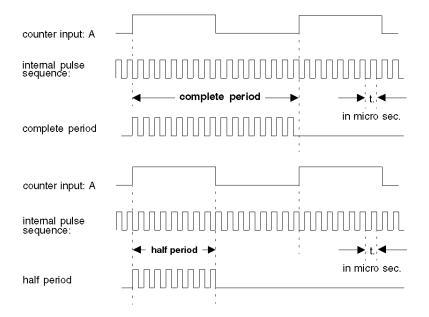

#### **Operating Mode 9: Period Meter with 5 Time Bases**

This operating mode measures the duration of a period. To do this the pulses are counted for the duration of the gate time. Various time bases can be selected according to the duration of the period. There are 5 time bases available, from 1ms to 10,000 ms.

This operating mode is used to acquire time measurements for processes.

**NOTE:** The time base should be chosen to achieve the desired accuracy and ensure the measuring time of the counter is not exceeded.

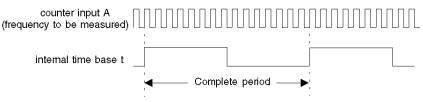

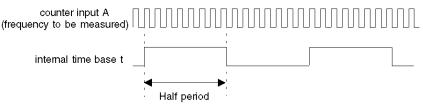

Full as well as half periods can be measured depending on the process.

Full period means the measurement of a series of pulses from positive to positive edge.

**NOTE:** Half period means the measurement of a series of pulses from positive to the next negative edge.

#### **Operating Mode A: Frequency Meter with 5 Time Bases**

In this operating mode the number of pulses per unit of time is measured. Various time bases can be selected according to the frequency to be measured. There are 5 time bases available, from 0.1 ms to 1000 ms.

**NOTE:** The time base should be chosen to achieve the desired accuracy and ensure the measuring time of the counter is not exceeded.

Full as well as half periods can be measured depending on the process.

- Full period means the measurement of a frequency from positive to positive edge of the time base.

- Half period means the measurement of a frequency from positive to negative edge of the time base.

Pulse diagram for full and half periods

#### Frequency measurement over a complete period

#### Frequency measurement over a half period

#### **Operating Modes for Absolute Encoder**

#### Absolute Encoder with SSI Protocol

Absolute encoders with SSI protocol can also be connected to both counters of the 170 AEC 920 00. A mixed operation with incremental encoders and absolute encoders is not possible.

The functions that deviate from the incremental encoder only are described below.

NOTE: In operating modes C, D and E the input filter must be switched off.

#### **Counter Resolution**

The resolution of the two count channels is either 12, 24, or 25 bit. This corresponds to decimal values from +4096 to +33 554 431.

The following operating modes are possible with absolute encoders:

- C = Counting with a resolution of 12 Bit (Single-turn Encoder)

- D = Counting with a resolution of 24 Bit (Multi-turn Encoder)

- E = Counting with a resolution of 25 Bit (Multi-turn Encoder)

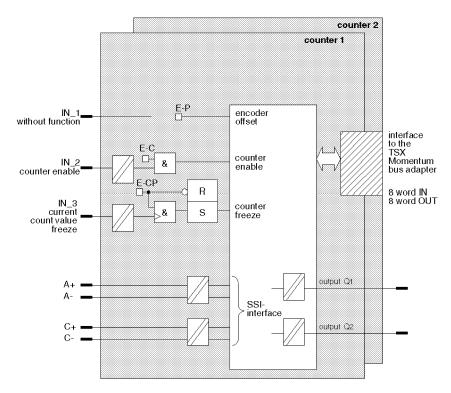

#### Encoder Offset

With the encoder offset the absolute position value of the encoder can be shifted. This shift is only permissible within the maximum encoder resolution. The defined offset is added to the current actual value through an 0->1 edge on Bit E\_P.

To make the absolute value of the encoder the machine zero point, the current actual position is transferred (negated) as the offset for the encoder. Through the addition of absolute value and offset carried out in the module, the actual value stands now at zero.

#### SSI = Synchronous Serial Interface

With the transfer of the absolute position, the absolute position data is transferred to a clock specified by the counter synchronously, beginning with the most significant bit (MSB).

The length of the data word may be 12 bit with single-turn encoders, and 24 or 25 bit with multiturn encoders. Evaluations of parity bits or power failure bits are not provided.

Clock signal cycle for data format

Each clock signal edge triggers the transmission of a data bit. The clock signal frequency is specified by the module and amounts to 250 kHz.

Clock signal and data signals stand at level 1 when non-operative. The current measurement is saved with the first falling edge. The data transmission occurs with the first rising edge.

After transmission of a data word, the data output stays at level 0 until the absolute encoder is ready for another measurement request (t). This time is dependent on the absolute encoder being used and amounts to approximately 30 microseconds.

### Count Channel for Counting Functions with Absolute Encoders

#### Absolute Encoder Function Display

The configured links for software and hardware show the correlations for absolute encoders.

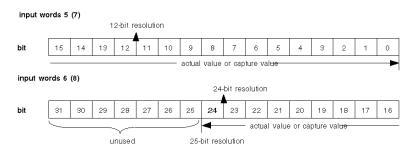

#### Operating Mode C: Channel Acquisition with Single-turn Encoders (SSI), 12-bit Resolution

Connection of an SSI encoder with one channel. The resolution amounts to 12 bits per rotation (single turn encoder).

Single turn encoders begin to count from 0 after one full rotation. They are suitable for procedures where the encoder does not use the whole rotation, or for applications where the number of rotations is not important (carousel, etc.).

See Up Counters (Mode 2) *(see page 104)* for an example of path evaluation with single-turn encoders.

#### Operating Mode D: Channel Acquisition with Multi-turn Encoders (SSI), 24-bit Resolution

The multi-turn encoder with 24-bit resolution delivers 12-bit resolution per rotation (4096 pulses), and can count 4096 rotations before overrunning. The advantage of the absolute encoder is that the absolute position is available immediately after it is switched on.

#### Operating Mode E: Channel Acquisition with Multi-turn Encoders (SSI), 25-bit Resolution

The multi-turn encoder with 25-bit resolution delivers 13-bit resolution per rotation (8192 pulses), and can count 4096 rotations before overrunning. The advantage of the absolute encoder is that the absolute position is available immediately after it is switched on.

See Up Counters (Mode 2) *(see page 104)* for an example of path evaluation with multi-turn encoders.

# Chapter 3 TSX Momentum Adapter

#### **Overview**

TSX Momentum is a modular system. Bus adapters and CPU adapters work in connection with an I/O unit as standalone modules. In order to function properly, each I/O unit must be equipped with an adapter.

The following two sections give an overview of the available CPU and bus adapters.

#### What Is in This Chapter?

This chapter contains the following topics:

| Торіс                                                   |  | Page |

|---------------------------------------------------------|--|------|

| TSX Momentum Bus Adapter                                |  | 38   |

| CPU Adapters and Interface Adapters of the TSX Momentum |  | 39   |

## **TSX Momentum Bus Adapter**

#### **Available Bus Adapters**

The bus adapters are used in the I/O units as interfaces for numerous, industry-standardized, open communication networks.

The following bus adapters are available:

| Model Number   | Purpose                                               |

|----------------|-------------------------------------------------------|

| 170 INT 110 00 | INTERBUS                                              |

| 170 NEF 110 21 | Modbus Plus, simple network cable and 984 data format |

| 170 NEF 160 21 | Modbus Plus, double network cable and 984 data format |

| 170 PNT 110 20 | Modbus Plus, simple network cable and IEC data format |

| 170 PNT 160 20 | Modbus Plus, double network cable and IEC data format |

| 170 DNT 110 00 | Profibus DP                                           |

| 170 FNT 110 00 | FIPIO for TSX 7 and April                             |

| 170 FNT 110 01 | FIPIO for TSX Premium                                 |

| 170 LNT 710 00 | DeviceNet                                             |

| 170 LNT 810 00 | ControlNet                                            |

| 170 ENT 110 00 | Ethernet                                              |

**NOTE:** Detailed Information about the individual bus adapters can be found in separate manuals. See Related Documents *(see page 9).*

# CPU Adapters and Interface Adapters of the TSX Momentum

### **CPU Adapters**

The CPU adapter can be compared to the central unit of a PLC that runs a user program and controls process I/O points. It can be plugged into this I/O unit to control its I/O points as local I/O.

| Model Number   | Internal Memory | Flash RAM  | Clocking Speed | Interfaces                |

|----------------|-----------------|------------|----------------|---------------------------|

| 171 CCS 700 00 | 64 Kbytes       | 256 Kbytes | 20 MHz         | 1 x RS-232                |

| 171 CCS 700 10 | 64 Kbytes       | 256 Kbytes | 32 MHz         | 1 x RS-232                |

| 171 CCS 760 00 | 256 Kbytes      | 256 Kbytes | 20 MHz         | 1 x RS-232<br>1 x I/O bus |

| 171 CCS 780 00 | 64 Kbytes       | 256 Kbytes | 20 MHz         | 1 x RS-232<br>1 x RS-485  |

| 171 CCS 780 10 | 512 Kbytes      | -          | 32 MHz         | 1 x RS-232<br>1 x RS-485  |

| 171 CCS 760 10 | 512 Kbytes      | -          | 32 MHz         | -                         |

The following four CPU adapters are available:

The functionality of the CPU adapter can be expanded using an interface adapter. The interface adapter is connected between the CPU adapter and the I/O unit.

Interface adapters offer:

- time

- battery buffering

- additional communication interfaces

**NOTE:** Interface adapters can only be used in connection with a CPU adapter and not with bus adapters.

Three different interface adapters are available:

| Model Number   | Interfaces                                                |

|----------------|-----------------------------------------------------------|

| 172 JNN 210 32 | 32 Modbus interface which are RS-232 or RS-485 compatible |

| 172 PNN 210 22 | a Modbus Plus interface                                   |

| 172 PNN 260 22 | Two (redundant) Modbus Plus interfaces                    |

**NOTE:** Further information about CPU adapters and interface adapters can be found in the *Momentum M1 Processor Adapter and Option Adapter User Guide.*

The dimensions of modules assembled together (with and without interface adapters) are given in the *Modicon Momentum I/O Base User Guide*.

# Part II Module Description

# Chapter 4 Structure of the 170 AEC 920

#### **Overview**

The following chapter provides an overview of the hardware structure of the fast counter module 170 AEC 920. Details of the wiring of the module and the signal assignments are described.

#### What Is in This Chapter?

This chapter contains the following topics:

| Торіс                                       | Page |

|---------------------------------------------|------|

| Internal Connections and Meaning of Signals | 44   |

| Wiring and Examples                         | 47   |

| LED Status Indicators                       | 53   |

| Technical Data                              |      |

| Selecting a Momentum Adapter                |      |

| Selection of Terminal Blocks                |      |

# Internal Connections and Meaning of Signals

#### I/O Unit

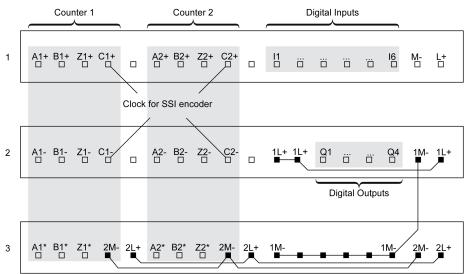

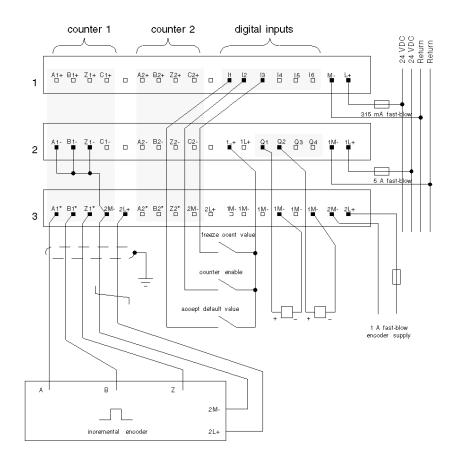

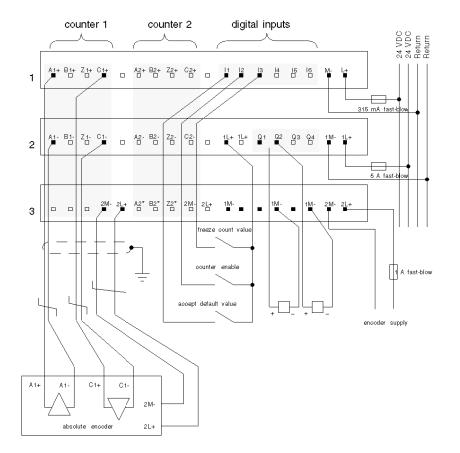

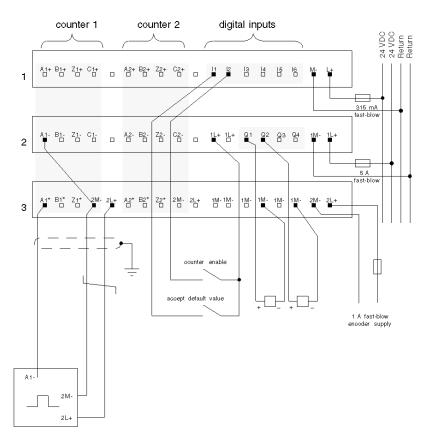

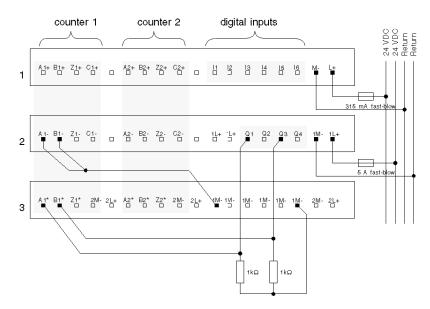

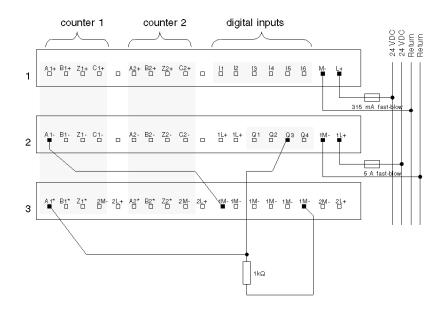

The figure below shows the internal connections of the I/O unit:

# A DANGER

### SHORT CIRCUIT AND/OR SPIKES

Install external fuses as protective measure according to the fuse values provided in the wiring diagrams

A module unprotected by a fuse can cause short circuit and/or spikes.

Failure to follow these instructions will result in death or serious injury.

## Assignment of Terminal Blocks

Connector 1

| Terminal number | Signal   | Function                                                              |

|-----------------|----------|-----------------------------------------------------------------------|

| 1, 6            | A1+, A2+ | Positive differential input A (5 V), counter channel 1, 2             |

| 2, 7            | B1+, B2+ | Positive differential input B (5 V), counter channel 1, 2             |

| 3, 8            | Z1+, Z2+ | Positive differential input Z (5 V), counter channel 1, 2             |

| 4, 9            | C1+, C2+ | Positive clock output for SSI, counter channel 1, 2                   |

| 11, 14          | 11, 14   | Digital inputs accept preset value, counter channel 1, 2              |

| 12, 15          | I1, I5   | Digital inputs counter enable, counter channel 1, 2                   |

| 13, 16          | 13, 16   | Digital inputs, freeze current counter value for counter channel 1, 2 |

| 17              | M-       | Supply voltage -return line                                           |

| 18              | L+       | Supply for module +24 VDC                                             |

## Connector 2

| Terminal number | Signal   | Function                                                                          |

|-----------------|----------|-----------------------------------------------------------------------------------|

| 1, 6            | A1-, A2- | Negative differential input A, counter channel 1, 2                               |

| 2, 7            | B1-, B2- | Negative differential input B, counter channel 1, 2                               |

| 3, 8            | Z1-, Z2- | Negative differential input Z, counter channel 1, 2                               |

| 4, 9            | C1-, C2- | Negative clock output for SSI, counter channel 1, 2                               |

| 13, 14          | Q1, Q2   | Digital output from counter channel 1                                             |

| 15, 16          | Q3, Q4   | Digital output from counter channel 2                                             |

| 17              | 1M-      | -Return (+ 24 VDC Switching Voltage)                                              |

| 11, 12, 18      | 1L+      | + 24 VDC Switching voltage for digital outputs, supply voltage for digital inputs |

#### Connector 3

| Terminal number | Signal   | Function                                                    |

|-----------------|----------|-------------------------------------------------------------|

| 1, 6            | A1*, A2* | Positive differential inputs A (24 V), counter channel 1, 2 |

| 2, 7            | B1*, B2* | Positive differential inputs B (24 V), counter channel 1, 2 |

| 3, 8            | Z1*, Z2* | Positive differential inputs Z (24 V), counter channel 1, 2 |

| 11 16           | 1M-      | -Return (+ 24 VDC Switching Voltage)                        |

| 4, 9, 17        | 2M-      | -Return (for encoder supply)                                |

| 5, 10, 18       | 2L+      | +5 +30 VDC supply voltage for encoder                       |

### Limit Frequencies and Cable Lengths for Incremental Encoders

Encoder type with signal level

| Signal level | Cable length                   | Limit frequency (kHz)     |

|--------------|--------------------------------|---------------------------|

| 5 V          | 100 m, shielded, twisted pairs | 200 kHz                   |

| 5 V          | 300 m, shielded, twisted pairs | 300 kHz                   |

| 24 V         | 300 m                          | 10 kHz (Filter activated) |

Limit frequencies and cable lengths for absolute encoders

| Encoder type with | Cable length | Limit frequency (kHz)                        |

|-------------------|--------------|----------------------------------------------|

| RS 422            | max. 100 m   | Each one is determined by the 170 AEC 920 00 |

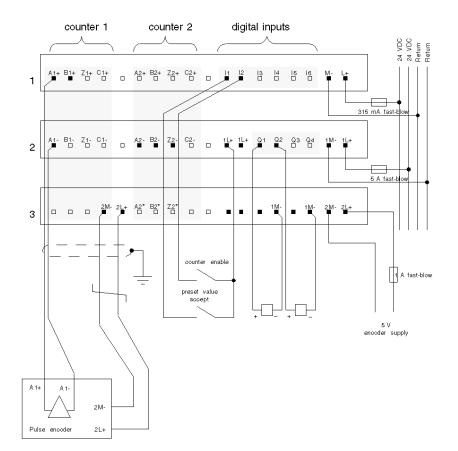

## Wiring and Examples

#### Hints for Wiring

To protect count signals from external interference in push-pull or common mode, we recommend the following measures:

- Use shielded, twisted pair cables with a minimum line diameter of 0.22mm, two for the count signals.

- Ground the cable shield.

- Assuming that the same grounding is used, the counter inputs of the I/O unit can be connected with a multi-lead cable (twisted pair), which also supplies the encoder.

- For the encoder supply (principally 5 V), take note that the voltage drop amounts to ca 0.35 V with a cable length of 100m, 1 mm 2 line diameter and an encoder current consumption of 100 mA.

- Keep encoder cables and power supply leads or similar sources of electrical interference separate (distance as much as possible >0.5 m).

- The supply for encoders and periphery should be drawn from separate sources to achieve isolation.

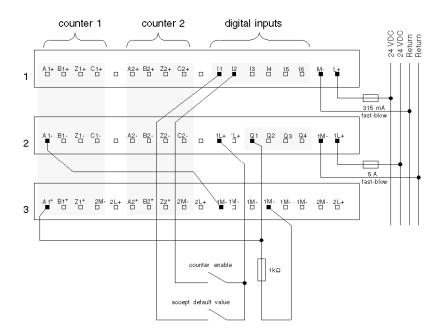

incremental encoder terminals or DIN plug Momentum terminals: series 4 3 2 1 1/A1 A1 . 1/A1-2/B1+ B1+ ٠ B1 2/B1-3/Z1+ Z1 Z1 . 3/Z1-5/2L+ 2L-4/2M 2M \*)

Example of connection of an incremental encoder for 5 V (counter 1)

\*) This link is established directly,

if the incremental encoder does not have a connection to ground.

Wiring example for pulse encoder (5 V)

Installation example for pulse encoder (24 V)

NOTE: The installation example refers to operating mode 1: down counting.

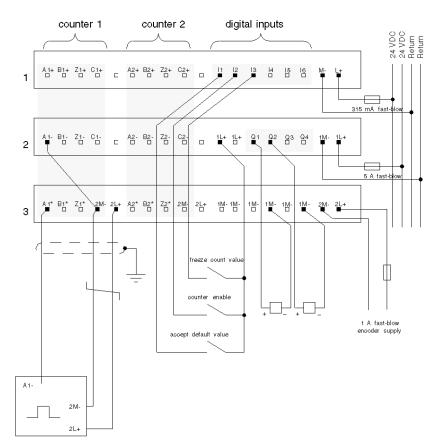

#### Installation example for incremental encoders (RS 422)

Installation for use as 24 V pulse encoder for A, B, and R line

NOTE: The installation example refers to operating modes 3, 4, and 5.

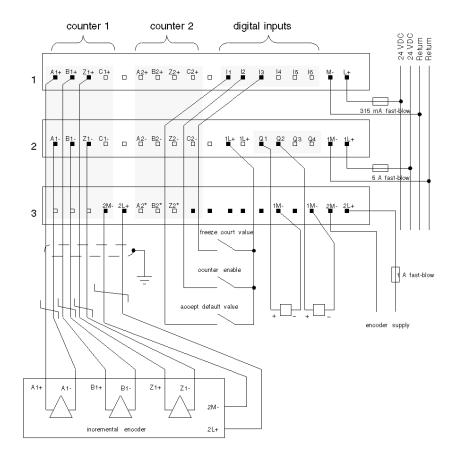

Installation example for absolute encoders with actuators

NOTE: The installation example refers to operating modes C, D, and E (absolute encoder SSI).

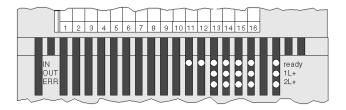

# **LED Status Indicators**

## LED Block

Front view of the LED block:

## LED meaning

| LED               | Status | Meaning                                                                                                      |  |

|-------------------|--------|--------------------------------------------------------------------------------------------------------------|--|

| ready             | green  | Ready for operation; supply voltage available for internal logic (5 V).                                      |  |

|                   | off    | lot ready for operation.                                                                                     |  |

| 1L+               | green  | Turn-on voltage 1L+ for digital outputs Q1 4 available.                                                      |  |

|                   | off    | Turn-on voltage 1L+ for digital outputs Q1 4 unavailable.                                                    |  |

| 2L+               | green  | Supply voltage for encoder 2L+(5 30V) available.                                                             |  |

|                   | off    | Supply voltage for encoder 2L+(5 30 V) 4 unavailable.                                                        |  |

| Top row<br>IN     | green  | Input status (depending on the LED input); input point active, i.e. "1" signal on the input (logic "ON").    |  |

| 11 16             | off    | Input status (depending on the LED input); input point inactive, i.e. "0" signal on the input (logic "OFF"). |  |

| OUT row<br>13 16  | green  | Output status (one LED per digital output); output active, i.e. 1-signal on the output (logic "ON").         |  |

|                   | off    | Output status (one LED per digital output); output inactive, i.e. 0-signal on the output (logic "OFF").      |  |

| Bottom row<br>ERR | red    | Digital outputs overloaded (one LED per output); short circuit or overload of the corresponding output.      |  |

| 13 16             | off    | Outputs Q1 Q4 function as normal.                                                                            |  |

# **Technical Data**

### **General Information**

General information for the 170 AEC 920 00:

| Type of module                                   | 2 quick counters (10 200 kHz)      |

|--------------------------------------------------|------------------------------------|

| Supply voltage, encoder supply, starting voltage | 24 VDC                             |

| Input current                                    | 6 mA at 24 VDC (Type 1+ or Type 2) |

| Max. load current                                | 0.5 A/Output                       |

| ID-Code for Interbus                             | 0633 hex1587 dec                   |

| Supply voltage                                   | 20 24 30 VDC                       |

| Current consumption                              | type. 200 mA at 24 VDC max. 350 mA |

| Power loss                                       | 4 W typical, 6 W maximum           |

## Digital Inputs (Help Inputs)

Layout of inputs:

| Encoder supply               | 24 V type., 30 V max.                                                                                                                            |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of Inputs             | 6                                                                                                                                                |

| Number of groups             | 2                                                                                                                                                |

| Input                        | <ul><li>3 for every counter with the functions:</li><li>a) accept preset value</li><li>b) Enable counter</li><li>c) Freeze count value</li></ul> |

| Type of signal               | True High                                                                                                                                        |

| IEC 1131 Type                | 1+                                                                                                                                               |

| Signal level for 1-signal    | +11 +30 VDC                                                                                                                                      |

| Signal level for 0-signal    | -3 +5 VDC                                                                                                                                        |

| Input current                | min. 2.6 mA for 1-Signal,<br>max. 1.2 mA for 0-Signal,                                                                                           |

| Voltage range for inputs     | -3 +30 VDC                                                                                                                                       |

| Surge                        | Surge 45 Vp for 10 ms                                                                                                                            |

| Input delay (output counter) | max. 1 ms off to on,<br>max. 1 ms on to off                                                                                                      |

## Counter Inputs (for Pulses)

Layout of counter inputs:

| Input types               | 5 VDC differential (RS422) or 24 VDC single ended |

|---------------------------|---------------------------------------------------|

| IEC 1131 Type             | 2                                                 |

| Count range (incremental) | 24 Bit plus sign (-16 777 216bis +16 777 215)     |

| (absolute)                | 25 Bit (0 to 33 554 431)                          |

#### 5 VDC differential

| Maximum count frequency    | 200 kHz           |

|----------------------------|-------------------|

| Input voltage for 1-signal | minimum 2.4 VDC   |

| Input current for 1-signal | > 3.7 mA          |

| Input voltage for 0-signal | maximum 1.2 VDC   |

| Input current for 0-signal | < 1 mA at 1.2 VDC |

## 24 VDC single ended

| Maximum count frequency    | 10 kHz             |

|----------------------------|--------------------|

| Input voltage for 1-signal | minimum 11 VDC     |

| Input current for 1-signal | > 6 mA             |

| Input voltage for 0-signal | -3 +5 VDC          |

| Input current for 0-signal | < 2 mA at <= 5 VDC |

## **Digital Outputs**

Layout of outputs:

| Output type          | Semi-conductor                                                                                     |

|----------------------|----------------------------------------------------------------------------------------------------|

| Switching voltage    | 20 24 30 VDC                                                                                       |

| Number of outputs    | 4                                                                                                  |

| Number of groups     | 2                                                                                                  |

| Switching current    | max. 0.5 A/Output                                                                                  |

| Type of signal       | True High                                                                                          |

| Leakage current      | < 0.5 mA at 24 VDC                                                                                 |

| Voltage drop when on | < 0.5 VDC at 0.5 A                                                                                 |

| Overload protection  | Outputs are protected against overloading and short circuits.                                      |

| Error display        | 1 red LED per output (row 3) for short circuits/overloading                                        |

| Error message        | Error message (I/O-error) for the bus-adapter, if the module is defect (self-test by the I/O unit) |

| Output delay for resistive load | max. 0.1 ms 0 -> 1, max. 0.1 ms 1 -> 0                                                 |

|---------------------------------|----------------------------------------------------------------------------------------|

| Maximum operation cycles        | 1 000/h inductive load<br>100/s resistive load<br>8/s Lamp load at 2.4 W               |

| Definable functions             | See Protective Measures, Certifications, and Mechanical Structure <i>(see page 56)</i> |

Clock output for absolute encoder:

| Output type                 | 5 VDC differential (RS 422) |

|-----------------------------|-----------------------------|

| Output voltage for 1-signal | >+/- 2 VDC                  |

| Output current for 1-signal | > 20 mA                     |

**NOTE:** If the outputs Q1 and/or Q3 are used as frequency outputs, the load must be at least 1kOhm.

#### Protective Measures, Certifications, and Mechanical Structure

Potential isolation between each other and against PE:

| -digital I/O signals, | 500 VAC for 1 min. |

|-----------------------|--------------------|

| -counter inputs,      |                    |

| -clock outputs,       |                    |

| -Supply voltage       |                    |

Safety devices:

| Internal                                | none                                                                                                          |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|

| External: Supply voltage L+             | 315 mA fast-blow (with bus adapter)                                                                           |

| External: Sensor and actuator supply1L+ | Depending on the design of the current consumption of the connected sensors and actuators, max. 5 A fast-blow |

| External: Encoder supply 2L+            | Depending on the design of the current consumption of the connected encoder, max. 1 A fast-blow               |

#### EMC for industrial use:

| Resistance to disturbance | IEC 1131 surge voltage in the network supply 500 V, 12 Ohm |  |

|---------------------------|------------------------------------------------------------|--|

| Emissions                 | EN 50081-2                                                 |  |

| Certifications            | UL, CUL, CSA, CE                                           |  |

#### Mechanical structure:

| Width                   | 125 mm                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------------|

| Depth (without adapter) | 40 mm                                                                                                   |

| Height                  | 141.5 mm without or with single bus bar<br>159.5 mm with double bus bar<br>171.5 mm with triple bus bar |

| Weight                  | 240 g                                                                                                   |

## Selecting a Momentum Adapter

#### **Bus/CPU Adapters**

Choose an appropriate bus or CPU adapter for your application and assemble it according to the instructions in the *Modicon Momentum I/O Base User Guide*.

# **A**CAUTION

#### ELECTRIC VOLTAGES PRESENT

Unplug the terminal blocks before separating the adapter from the I/O unit. The I/O unit will be then be dead.

This can be ensured by connecting the terminal blocks only after first assembling the adapter.

When the I/O unit is connected to the power supply, electrical voltages are present. Make sure that there is no voltage present while the I/O unit has no adapter.

Failure to follow these instructions can result in injury or equipment damage.

## **Selection of Terminal Blocks**

### Overview

For the connection of encoders as well as sensors and actuators to the I/O unit, suitable terminal blocks must be acquired. These can be found in the *TSX Momentum I/O Base User Guide*.

# Part III Configuration

#### **Overview**

This part deals with the configuration of the fast counter module 170 AEC 920 00. The DFB block AEC is described and a configuration example is given for each operating mode.

#### What Is in This Part?

This part contains the following chapters:

| Chapter | Chapter Name                         |     |

|---------|--------------------------------------|-----|

| 5       | Configuration of Output Words        | 63  |

| 6       | Status Messages and Count Values     | 87  |

| 7       | 7 Parameter Setting of the AEC Block |     |

| 8       | Application Examples                 | 103 |

# Chapter 5 Configuration of Output Words

#### **Overview**

By setting parameters for the output words, the counting functions, output configuration, and default values for the count channels of the 170 AEC 920 00 module are set.

To simplify open project creation, the functions of the output words for each bit will be explained.

#### What Is in This Chapter?

This chapter contains the following topics:

| Торіс                            | Page |

|----------------------------------|------|

| Configuration                    | 64   |

| Summary of the Output Words      | 66   |

| Configuring Output Words 1 and 2 | 67   |

| Configuring Output Words 3 and 4 | 74   |

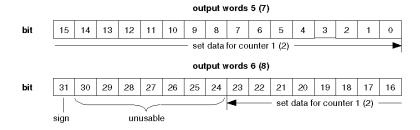

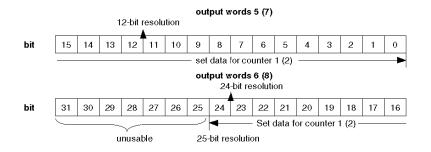

| Data in Output Words 5/6 and 7/8 | 85   |

| File Format of Set Data          | 86   |

# Configuration

#### **Output Words**

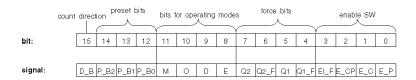

The eight output words for the counter are sent from the bus master to the I/O module with the following configuration data:

#### Address 4x: Output word 1

Configuration for counter 1

#### Address 4x +1: Output word 2

| 15 | 14 | 13 | 12 | <br>10 | ٥ | 9 | 7 | 6 | 5 | 4 | 3 | 2 | 4 | 0 |

|----|----|----|----|--------|---|---|---|---|---|---|---|---|---|---|

| 10 | 14 | 10 | 12 |        | 3 | 0 | 1 | 0 | 5 | - | 5 | ~ |   |   |

| _  | ~  |    |    |        |   |   |   |   |   |   |   |   |   |   |

Configuration for counter 2

#### Address 4x +2: Output word 3

|  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|--|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

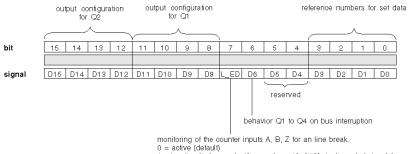

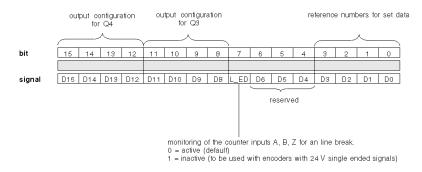

| Configuration of the digital outputs |  |

|--------------------------------------|--|